# DS2290 T1 Isolation Stik

DS2290

#### **FEATURES**

- Protected interface for connecting equipment to T1 lines

- Provides 800 volts of surge protection and 1500 volts of isolation

- FCC Part 68 registered

- Meets TR 62411 and T1.403–1989 for transmit pulse characteristics

- Line build outs of 0, -7.5, and -15 dB

- Companion to the DS2291 T1 Long Loop Stik

- Connects to a standard 30–pin single in–line connector

- Single +5V supply

- Compatible with the DS2180A and DS2141A T1 Tranceivers

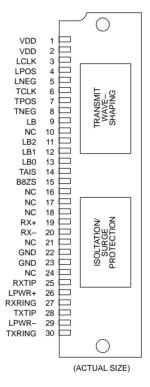

### PIN ASSIGNMENT

#### DESCRIPTION

The DS2290 T1 Isolation Stik provides all the surge and isolation protection that is necessary to connect a piece of equipment to a T1 line. It offers a function similar to that provided by a Data Access Arrangement (DAA) when a modem is connected to a phone line. The DS2290 is FCC Part 68 pre–registered so the user can connect equipment to T1 lines without any further testing or qualification. It contains onboard waveshaping

circuitry that creates transmit pulses meeting the latest T1 specifications including TR 62411 (Accunet\* T1.5 Service Description and Interface Specifications, – December 1990) and T1.403–1989 (Carrier to Carrier Installation – DS1 Metallic Interface). Applications include Channel Service Units and similar equipment that requires a fully protected interface.

\* Service mark of AT&T Communications

022798 1/9

#### OVERVIEW

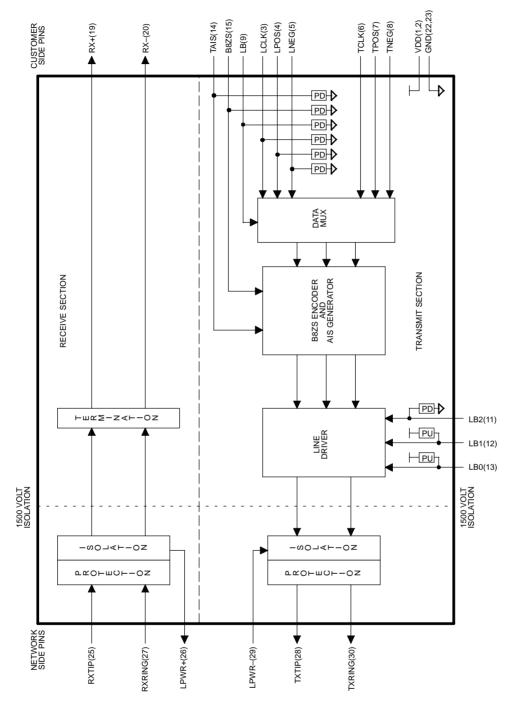

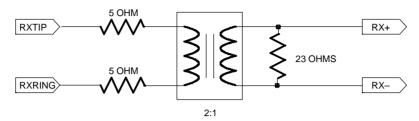

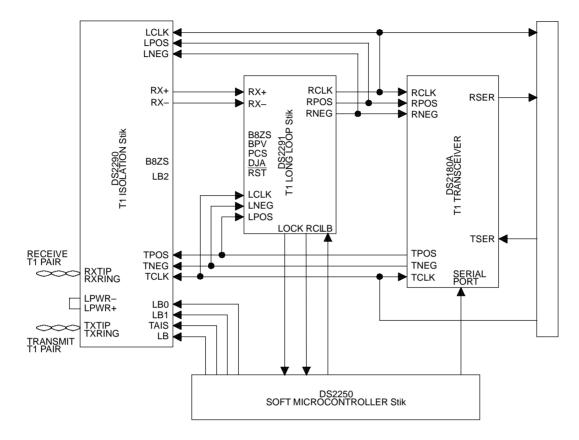

The DS2290 contains all the isolation and surge protection required to connect equipment to T1 lines. The Isolation Stik has a receive and a transmit section. (See Figure 1.) In the receive section, inputs RXTIP and RXRING are connected directly to the receive T1 twisted pair. These inputs are terminated at 100 ohms. The T1 signal received at RXTIP and RXRING is coupled through a 2:1 transformer and presented at the RX+ and RX- outputs. See Figure 2. There is a full 1500 volts of isolation between the Network Side pins and the Customer Side pins.

In the transmit section, data that is to be transmitted is sourced from either the TPOS and TNEG inputs or the LPOS and LNEG inputs. The Data Mux will transmit data at the TCLK rate from the TPOS and TNEG inputs if the LB pin is either tied low or left open. It will transmit data at the LCLK rate from the LPOS and LNEG inputs if the LB pin is tied high. In order to comply with the latest T1 standards, the clock presented at either TCLK or LCLK must be at a 1.544 MHz rate (±32 ppm) and must not jitter beyond 0.05 unit intervals peak-to-peak (UIpp). TPOS and TNEG can be tied together if the source of the transmit data is in a NRZ format. The DS2290 will automatically sense that these inputs are tied together and will create a bipolar data stream from them. The same holds true for the LPOS and LNEG inputs.

Data out of the Data Mux is passed to a B8ZS encoder and AIS generator. If the B8ZS pin is tied high, then the DS2290 will properly encode the transmit data stream for the B8ZS zero code suppression scheme. If the B8ZS pin is tied low or left open, the DS2290 will not encode the transmit data for B8ZS. Also, the DS2290 can be configured to transmit an AIS (Alarm Indication Signal). If the TAIS pin is tied high, the DS2290 will transmit an unframed, all ones signal at either the TCLK (LB=0) or LCLK (LB=1) rate.

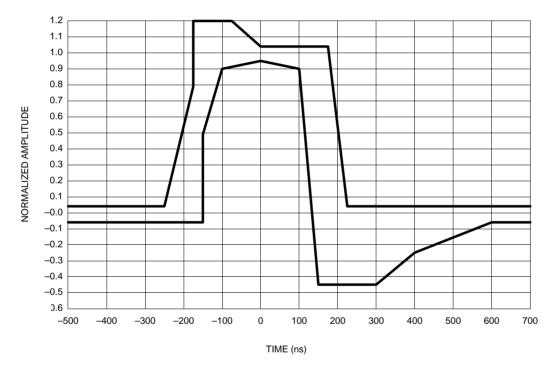

The data to be transmitted is fed to the line driver. The line driver creates the T1 pulse that will be transmitted. The line build out pins LB0 to LB2 select whether the output pulse level will be 0, -7.5, or -15 dB (see Table 3). If 0 dB of build out is selected, the output pulse will conform to the shape described in Figure 2. This pulse shape is congruent with the latest T1 specifications such as TR 62411 and T1.403–1989. If the -7.5 dB or -15 dB line build outs are selected, then the pulse shown in Figure 3 will be attenuated according to the transfer function as described in FCC Part 68, Subpart D. Once the T1 pulse has been created, it is then transmitted onto the transmit T1 twisted pair via the TTIP and TRING outputs.

The DS2290 contains provisions for line powering. If the DS2290 is to be powered from the T1 line using a DC simplex power arrangement, then an external DC-to-DC converter can connected to the LPWR+ and LPWRpins. Requirements for line powering are currently being relaxed and will be totally removed in the future. If the DS2290 is not line powered, the LPWR+ and LPWR- pins should be tied together.

Figure 4 shows a typical application using the DS2290. The transmit and receive T1 twisted pairs are connected directly to the DS2290. The DS2291 T1 Long Loop Stik recovers clock and data from the protected signal provided by the Isolation Stik. The DS2180A T1 Transceiver frames to the recovered data and interfaces to the system backplane. The DS2250 Soft Microcontroller Stik is used to control and monitor the status of the other devices.

022798 2/9

# DS2290 BLOCK DIAGRAM Figure 1

022798 3/9

# DS2290 RECEIVE SECTION CIRCUITRY Figure 2

# **OUTPUT PULSE TEMPLATE** Figure 3

022798 4/9

## TYPICAL DS2290 APPLICATION Figure 4

### NETWORK SIDE PIN DESCRIPTION Table 1

| PIN      | SYMBOL          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                         |

|----------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25<br>27 | RXTIP<br>RXRING | I   | <b>Receive Tip and Ring Inputs.</b> Connects directly to the receive T1 twisted pair. These inputs are transformer coupled and terminated at 100 ohms. See Figure 2.                                                                                                                |

| 28<br>30 | TXTIP<br>TXRING | 0   | <b>Transmit Tip and Ring Outputs.</b> Connects directly to the transmit T1 twisted pair. Output signal level is programmable via the LB0 to LB2 pins. (See Table 3.)                                                                                                                |

| 26<br>29 | LPWR+<br>LPWR-  | _   | <b>Loop Power Connections.</b> These pins connect to the internal center–taps of the transmit and receive transformers. They provide access to the DC power on the T1 line (may not be provided by carriers in the future). Tie together if no simplex power arrangement is needed. |

DS2290

| PIN            | SYMBOL            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2            | V <sub>DD</sub>   | -   | Positive Supply. 5.0 Volts.                                                                                                                                                                                                                                                                                                |

| 3              | LCLK              | I   | <b>Loopback Clock.</b> Clock for loopback data. Internally pulled low by $100K\Omega$ .                                                                                                                                                                                                                                    |

| 4<br>5         | LPOS<br>LNEG      | I   | <b>Loopback Bipolar Data.</b> Sampled on the falling edge of LCLK if LB is tied high. Internally pulled low by $100K\Omega$ .                                                                                                                                                                                              |

| 6              | TCLK              | I   | Transmit Clock. Apply a 1.544 MHz (±32 ppm) clock here.                                                                                                                                                                                                                                                                    |

| 7<br>8         | TPOS<br>TNEG      | I   | <b>Transmit Bipolar Data.</b> Data that is to be transmitted. Sampled on the falling edge of TCLK when LB is tied low or left open. TPOS and TNEG can be tied together for an NRZ data input.                                                                                                                              |

| 9              | LB                | I   | <b>Loopback Enable.</b> Tie high to transmit data from LPOS and LNEG; tie low or leave open to transmit data from TPOS and TNEG. Internally pulled low by 100K ohm.                                                                                                                                                        |

| 11<br>12<br>13 | LB2<br>LB1<br>LB0 | I   | <b>Line Build Out Select.</b> State determines whether the transmitted signal has $0, -7.5, \text{ or } -15 \text{ dB of line build out.}$ See Table 3. LB0 and LB1 are internally pulled high by $100K\Omega$ ; LB2 is pulled low by $100K\Omega$ . If all three build out pins are left open, the default state is 0 dB. |

| 14             | TAIS              | I   | <b>Transmit Alarm Indication Signal.</b> Tie high to transmit an unframed all ones signal at either the TCLK (LB=0) or LCLK (LB=1) rate. Internally pulled low by $100K\Omega$ .                                                                                                                                           |

| 15             | B8ZS              |     | <b>B8ZS Enable.</b> Tie high to enable B8ZS encoding; tie low or leave open to disable B8ZS encoding. Internally pulled low by $100K\Omega$ .                                                                                                                                                                              |

| 19<br>20       | RX+<br>RX–        | 0   | Receive Analog Output. Protected differential T1 signal output here.                                                                                                                                                                                                                                                       |

| 22,23          | GND               | _   | Ground. 0.0 volts.                                                                                                                                                                                                                                                                                                         |

### **CUSTOMER SIDE PIN DESCRIPTION** Table 2

NOTE: Do not connect any signal to pins 10, 16, 17, 18, 21, and 24.

### LINE BUILD OUT SELECTS Table 3

| LINE BUILD OUT SELECTS | LB0 | LB1 | LB2 |

|------------------------|-----|-----|-----|

| 0 dB                   | 1   | 1   | 0   |

| -7.5 dB                | 1   | 0   | 0   |

| –15 dB                 | 0   | 1   | 0   |

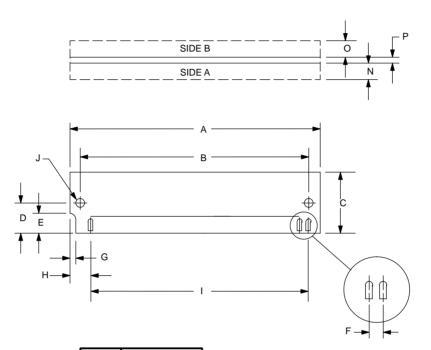

### SINGLE IN-LINE CONNECTOR

The DS2290 is designed to connect directly into a 30–position single in–line connector. These connectors are available from a number of vendors.

#### 022798 6/9

ABSOLUTE MAXIMUM RATINGS\* Voltage on any Pin Relative to Ground (Customer Side pins only) Operating Temperature Storage Temperature

-0.3V to V<sub>CC</sub> + 0.3V

0°C to 70°C -55°C to +125°C

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| RECOMMENDED DC OPERAT | (C              | )°C to 70°C) |     |                      |       |       |

|-----------------------|-----------------|--------------|-----|----------------------|-------|-------|

| PARAMETER             | SYMBOL          | MIN          | TYP | MAX                  | UNITS | NOTES |

| Logic 1               | VIH             | 2.0          |     | V <sub>CC</sub> +0.3 | V     | 3     |

| Logic 0               | V <sub>IL</sub> | -0.3         |     | +0.8                 | V     | 3     |

| Supply                | V <sub>DD</sub> | 4.75         |     | 5.25                 | V     |       |

## CAPACITANCE

| CAPACITANCE        |                  |     |     |     |       | (t <sub>A</sub> =25°C) |

|--------------------|------------------|-----|-----|-----|-------|------------------------|

| PARAMETER          | SYMBOL           | MIN | ТҮР | MAX | UNITS | NOTES                  |

| Output Capacitance | C <sub>IN</sub>  |     | 30  |     | pF    | 3                      |

| Output Capacitance | C <sub>OUT</sub> |     | 50  |     | pF    | 3                      |

#### DC ELECTRICAL CHARACTERISTICS

(0°C to 70°C; V<sub>DD</sub>=5V  $\pm$  5%)

| PARAMETER             | SYMBOL          | MIN  | ТҮР | MAX  | UNITS | NOTES |

|-----------------------|-----------------|------|-----|------|-------|-------|

| Supply Current        | I <sub>DD</sub> |      | 60  | 80   | mA    | 1     |

| Input Leakage         | lı –            | -100 |     | +100 | μA    | 2,3   |

| Output Current (2.4V) | I <sub>ОН</sub> | -1.0 |     |      | mA    | 3     |

| Output Current (0.4V) | I <sub>OL</sub> | +4.0 |     |      | mA    | 3     |

## NOTES:

1. TCLK = 1.544 MHz; V<sub>DD</sub> = 5.25V; outputs open; driving all ones into 6000 feet of 22 AWG.

2.  $V_{SS} < V_{IN} < V_{DD}$ .

3. Does not apply to any of the network side pins nor RX+ or RX-.

#### DS2290

#### ANALOG ELECTRICAL CHARACTERISTICS

## (0°C to 70°C; V<sub>DD</sub>=5V $\pm$ 5%)

| PARAMETER                                      | SYMBOL            | MIN | ТҮР | МАХ  | UNITS | NOTES |

|------------------------------------------------|-------------------|-----|-----|------|-------|-------|

| Input Impedance at RXTIP and RXRING at 772 KHz | Ι <sub>Ζ</sub>    | 95  | 100 | 105  | ohms  | 1     |

| Transmit Jitter Generation                     | J <sub>GEN</sub>  |     |     | 0.03 | Ulpp  | 2     |

| Transmit Pulse Amplitude                       | P <sub>AMP</sub>  | 2.5 | 3.0 | 3.5  | Vpk   | 3,4,5 |

| Pulse Width Balance @ 50%                      | PW <sub>BAL</sub> |     | 1   | 10   | ns    | 3,6   |

| Pulse Amplitude Balance                        | PA <sub>BAL</sub> |     | 10  | 100  | mV    | 3,6   |

| Power Level at 772 KHz                         | P <sub>LVL</sub>  | 12  |     | 19   | dBm   | 7     |

## NOTES:

- 1. RX+ and RX- left open circuited.

- 2. Jitter present at TXTIP and TXRING with no jitter at TCLK (LB=0) or LCLK (LB=1).

- 3. Measured with 100 ohm (±5%) termination at TXTIP and TXRING.

- 4. Measured directly at TXTIP and TXRING with 0 dB of line build out.

- 5. Pulse shape meets template in Figure 3 over temperature and voltage.

- 6. Measured over 17 consecutive pulses.

- 7. Measured in a 2 KHz to 3 KHz band about 772 KHz; power level in a 2 to 3 KHz band at 1.544 MHz is at least 25 dB lower.

| DIGITAL ELECTRICAL CHARA                                           | (0°C to 70°C; V <sub>DD</sub> =5V $\pm$ 5%) |     |     |     |       |       |

|--------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|-------|-------|

| PARAMETER                                                          | SYMBOL                                      | MIN | ТҮР | MAX | UNITS | NOTES |

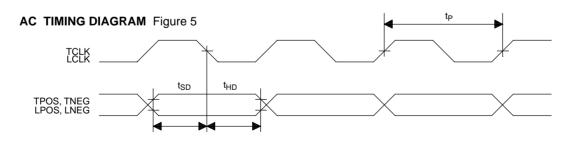

| TCLK Period                                                        | t <sub>P</sub>                              |     |     | ±32 | ppm   | 1     |

| TPOS, TNEG or LPOS, LNEG<br>Setup Time to TCLK or LCLK<br>Falling  | t <sub>SD</sub>                             | 50  |     |     | ns    |       |

| TPOS, TNEG or LPOS, LNEG<br>Hold Time from TCLK or LCLK<br>Falling | t <sub>HD</sub>                             | 50  |     |     | ns    |       |

### **DIGITAL ELECTRICAL CHARACTERISTICS**

## NOTE:

1. Necessary to meet current carrier and FCC specifications.

022798 8/9

| PKG   | 30-1  | PIN   |  |  |

|-------|-------|-------|--|--|

| DIM   | MIN   | МАХ   |  |  |

| A IN. | 3.455 | 3.505 |  |  |

| B IN. | 3.229 | 3.239 |  |  |

| C IN. | 0.845 | 0.855 |  |  |

| D IN. | 0.395 | 0.405 |  |  |

| E IN. | 0.245 | 0.255 |  |  |

| F IN. | 0.100 | BSC   |  |  |

| G IN. | 0.075 | 0.085 |  |  |

| H IN. | 0.295 | 0.305 |  |  |

| I IN. | 2.900 | BSC   |  |  |

| J IN. | 0.120 | 0.130 |  |  |

| N IN. |       | 0.235 |  |  |

| O IN. |       | 0.100 |  |  |

| P IN. |       | 0.054 |  |  |

DS2290

022798 9/9